在我們的損傷層檢測分析服務中,已介紹過晶棒與晶片的損傷層分析流程與檢測方式。本篇將進一步針對矽電極柱的損傷層檢測技術進行詳盡說明。

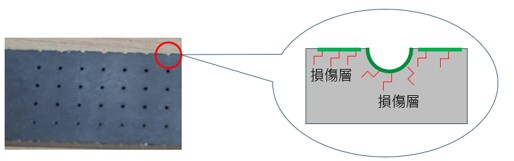

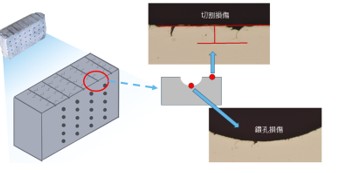

如下圖(圖一)所示,即為我們此次的觀察對象—矽電極柱。從圖片中可以清楚看出表面經鑽孔、加工後留下的孔洞、凹槽及切割痕跡,而這些位置皆為損傷層可能出現的區域(圖二)。

圖一、矽電極柱

圖二、損傷層示意圖

矽電極柱是一種經由高精度加工製成的柱狀矽材料,常應用於電化學元件、能源儲存設備、或半導體相關零組件中。其設計通常具備多孔、高表面積的特性,以提升導電效率或反應表面積。

在加工過程中,因切割、鑽孔等機械作用,容易造成表面或次表層結構的破壞,如微裂縫、塑性變形或非晶化等情況,這些破壞區域即稱為損傷層。

在矽電極柱表面,損傷層常見於以下區域:

這些損傷若未及早發現,可能影響後續製程良率、導電性能,甚至降低產品使用壽命。

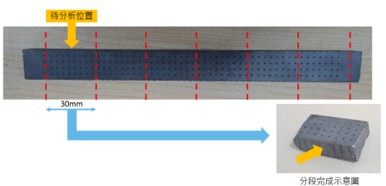

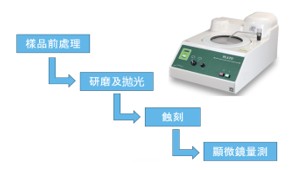

要觀察這些損傷層,我們需先將樣品進行適當的分段處理(圖三),將欲觀察區域裁切成合適大小,再依序進行以下作業流程(圖四):

圖三、分段作業

圖四、作業程序

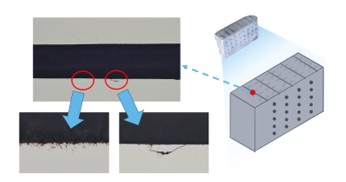

完成處理後,即可在溝槽等區域觀察到深度從數十微米至數百微米不等的損傷層(圖五)。從側面觀察,也可清楚辨識損傷層的厚度與範圍(圖六)。

這些分析有助於判定機械加工對材料所造成的影響,進而改善製程參數或預防瑕疵發生。

圖五、溝槽損傷層

圖六、側面分析損傷

機械加工所造成的損傷,是導致零組件壽命縮短與良率降低的主要原因之一。雖難以完全避免,但透過精確的損傷層分析,我們能:

上濰科技具備豐富的半導體材料、零組件與耗材損傷層檢測經驗,能協助客戶:

未來我們也將持續分享更多真實案例與分析經驗,敬請期待!

諮詢信箱 x

諮詢信箱 x